The chapter key highlights are the detail description for the synchronizers, data path, and control path synchronization logic using the efficient Verilog RTL. This chapter focuses in the key design techniques which are used to describe the multiple clock domain designs while passing data from one of the clock domain to other. These kinds of designs need to be described using the efficient design architectures and Verilog RTL. It shows how the design rule checks and features in Vivado help automate this flow for the user. Hence, it has been proven effective and highly successful in increasing the TDF test frequency to the highest operating clock domain frequency of the design.In the practical ASIC and SOC designs the multiple clocks are used and the designs are called as multiple clock domain designs. This video shows how a design with multiple clock domains can be assembled using Vivado IP Integrator. In an experimental 200 M-transistor and 4-clock-domains test-chip netlist, this methodology is able to identify clock sources for all registers in five minutes time, and that processing time is negligible when compared to the TDF automatic test pattern generation (ATPG) time. It identifies all user registers in the design and recursively identifies the clock sources of those registers through intelligent net connectivity analysis. The methodology advocated in this paper aims to overcome this bottleneck by introducing an automated yet comprehensive approach to segregate and consolidate the various clock domains in any design for more effective TDF testing. Despite transition delay fault (TDF) tests providing reasonable coverage against DSM marginal defects, this methodology is hampered in designs with multiple clock domains where the lowest operating clock frequency becomes the dominant TDF testing frequency. With the rapid advancement of fab process technology into the nanometer node era, there is an increasing trend in the manifestation of deep submicron (DSM) marginal defects in integrated circuit (IC) fabrication. © Springer Science+Business Media, LLC 2009.

Multiclock domain verification#

Static Timing Analysis for Nanometer Designs serves as a reference for a graduate course in chip design and as a text for a course in timing verification for working engineers. proposed algorithms to identify false the multi-clock-domain mapping process. Professionals who are beginning to use static timing analysis or are already well-versed in static timing analysis will find this book useful. A multi-cycle path and a FPGA technology mapping with multi-clock domains. This book is written for professionals working in the area of chip design, timing verification of ASICs and also for graduate students specializing in logic and chip design. Appendices provide complete coverage of SDC, SDF, and SPEF formats.

Multiclock domain full#

Verification of hierarchal building blocks, full chip, including timing verification of special IO interfaces are covered in detail. Timing checks at various process, environment, and interconnect corners, including on-chip variations, are explained in detail.

The relevant topics such as cell and interconnect modeling, timing calculation, and crosstalk, which can impact the timing of a nanometer design are covered in detail. This book provides a blend of underlying theoretical background and in-depth coverage of timing verification using static timing analysis.

Multiclock domain free#

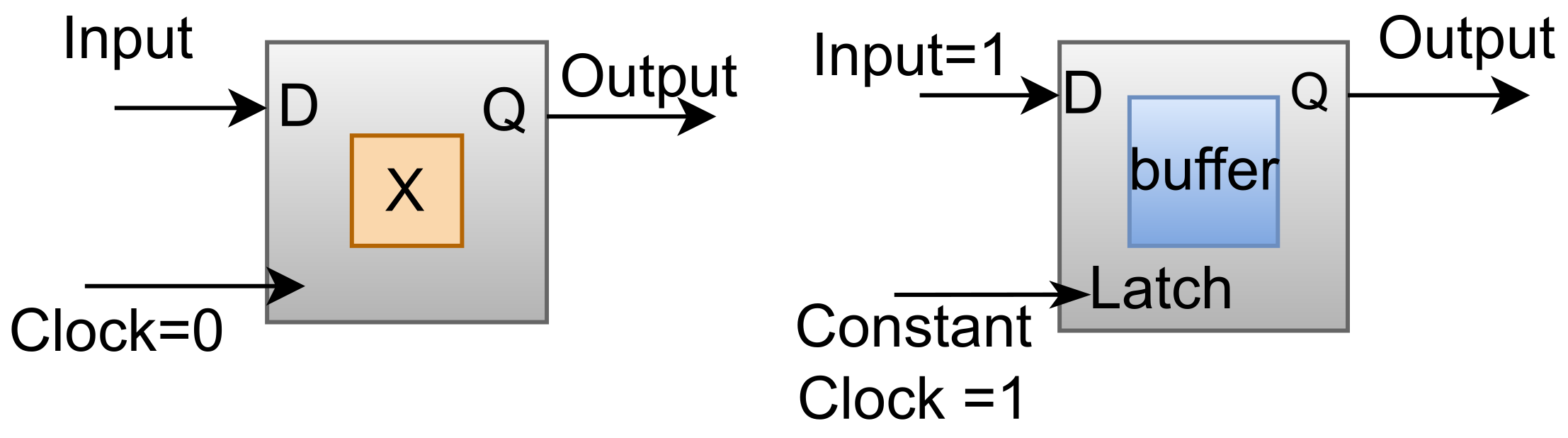

If the flip-flops are triggered by the different clock sources then the design is said to be asynchronous clock domain design. Ashley Productions Time Zone 12' Advanced Instruction Clock by Ashley Productions 67.99 Free shipping 10' Wall Clock by La Crosse Technology 82.99 ( 2) Free shipping Sale Ashley Productions Time Zone 12' Instruction Clock by Ashley Productions 67.99 Free shipping Weese 16' Wall Clock by Symple Stuff 92.99 ( 23) Free shipping More Options. If all the flip-flops in the design are clocked by single clock source then the design is said to be synchronous. Static Timing Analysis for Nanometer Designs: A Practical Approach is a reference for both beginners as well as professionals working in the area of static timing analysis for semiconductors. 13.1 What Is Multiple Clock Domain It is a very simple approach to design single clock domain design logic.

0 kommentar(er)

0 kommentar(er)